Laporan Akhir 1

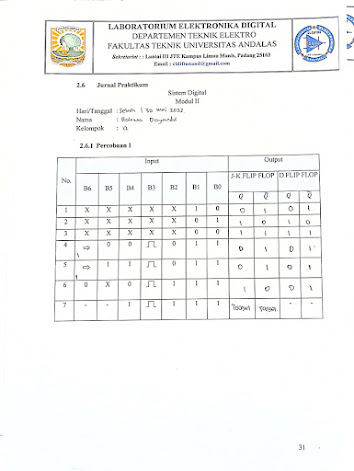

(Percobaan 1 J-K flip flop dan D flip flop)

2. Alat dan Bahan

[Kembali]

a.. Jumper

Gambar 1. Jumper

- J-K Flip-Flop

Pada rangkaian J-K Flip-Flop di dalamnya juga terdapat R-S Flip-Flop, hal ini dikarenakan J-K Flip-Flop merupakan pengembangan dari R-S Flip Flop. Dapat dilihat bahwa input yang masuk ke J=0 dan input K=0 dan pada kaki CLK diberi clock. Dimana sesuai dengan kondisi yang telah dipilih bahwasannya input masukan pada R berlogika 1 dan S berlogika 1, maka disini R-S Flip-Flop akan tidak aktif karena R-S Flip-Flop bekerja pada aktif low yang mana akan aktif jika berlogika 0 dan mengakibatkan output yang dihasilkan Q=0 dan Q`=1

Bisa dilihat pada kondisi 1 kondisi B0(R)=0, B1(S)=1, B2(J)=don't care, B3(CLK)=don't care, B4(K)=don't care. Maka output pada Q dan Q’ adalah Q =0 dan Q’ =1. Begitupun dengan percobaan variasi lainnya sesuai dengan jurnal.

- D Flip-Flop

Pada rangkaian D Flip-Flop sesuai dengan kodisi yang telah dipilih B5 berlogika 0, dan B6 berlogika 0, maka yang bekerja adalah R-S Flip-Flopnya karna input yang masuk berlogika 0, jadi apapun yang dilakukan pada input masukan D tidak akan mempengaruhi output dari rangkaiannya, jadi pada percobaan kami, didapatkan D nya itu berlogika 0, maka output yang dihasilkan yaitu Q nya berlogika 0, dan Q' berlogika 1.

Bisa dilihat pada kondisi 1 dimana B0(R)=0, B1(S)=1, B5(D)=don't care, dan B6(CLK)=don't care. Maka output yang pada Q dan Q’ adalah Q=0 dan Q'=1. Begitupun dengan percobaan variasi lainnya sesuai dengan jurnal.

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke CLOCK dan K berlogika 1 digambarkan timing diagramnya ?

jawab:

Jika rangkaian diatur pada input B3 dan B2 dihubungkan ke CLOCK maka output Q akan berlogika 0 dan Q' akan berlogika 1 apabila komponen rangkaian R, S, dan J berlogika 1.

Timing diagram:

2. Analisa apa yang terjadi saat B5 dan B6 dihubungkan ke CLOCK dan gambarkan timing diagramnya!

jawab:

Jika rangkaian percobaan 1 B5 dan B6 nya dihubungkan ke CLOCK maka output W akan berlogika 1 karena input pada D berlogika 1 (aktif) apabila CLOCK juga berlogika 1 dan output Q tidak berubah jika CLOCK berlogika 0 (off).

Timing diagramnya:

.png)

.png)

Komentar

Posting Komentar